Télécharger le fichier pdf d’un mémoire de fin d’études

Capteurs

Microcontrôleur

Stockage de l’énergie

|

Table des matières

Publications liées au manuscrit

I État de l’art et modélisation 1

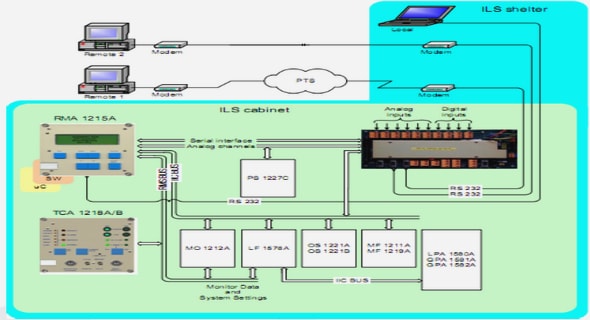

1 Marché actuel de l’IoT, architecture des réseaux de communication, applications et nœuds de capteurs communicants

1.1 Marché actuel et prédictions autour de l’Internet des objets

1.2 Représentation globale des réseaux de communication

1.3 Quelles applications pour les nœuds de capteurs ?

1.4 Synthèse

1.5 Nœuds de capteurs sans fil

1.6 Architecture du nœud de capteurs

1.6.1 Radios

1.6.2 Capteurs

1.6.3 Microcontrôleur

1.6.4 Récupérateurs d’énergie

1.6.5 Stockage de l’énergie

1.6.6 Module de gestion de l’énergie

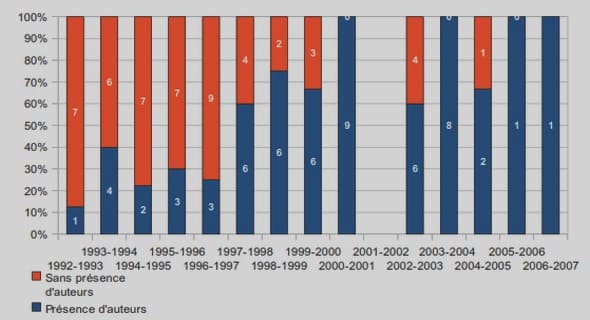

1.7 Historique des réalisations de nœuds de capteurs complets

1.7.1 Démonstrateurs de laboratoires

1.7.1.1 Nœuds de taille millimétrique

1.7.1.2 Nœuds de taille centimétrique

1.7.2 Nœuds de capteurs commerciaux

1.7.3 Synthèse

2 Microcontrôleurs pour nœuds de capteurs sans fil

2.1 Architecture des microcontrôleurs

2.1.1 Architecture globale d’un microcontrôleur

2.1.2 Cœur de processeur

2.1.3 Mémoires

2.1.3.1 Mémoire Volatile

2.1.3.2 Mémoire Non Volatile

2.1.4 Horloge

2.1.5 Module de sécurité et autres accélérateurs matériels

2.1.6 Unité de gestion de l’énergie et des horloges

2.1.7 Périphériques

2.2 Réalisations de microcontrôleurs

2.2.1 Système sur puce de laboratoires

2.2.2 Système sur puce commerciaux

2.3 Pourquoi réduire la consommation du microcontrôleur et pour quelles applications ?

2.4 Synthèse

3 Perspectives de réduction de la consommation pour le sous système de traitement et de contrôle du nœud

3.1 Augmenter la flexibilité d’un système et réduire sa consommation par des solutions architecturales

3.2 Réduire la consommation d’un système par une gestion intelligente de l’énergie 40

3.3 Augmenter la flexibilité d’un système et réduire sa consommation par la technologie

3.3.1 Polarisation arrière de la technologie UTBB FDSOI

3.3.2 La technologie UTBB FDSOI près du seuil

3.3.3 Élargissement de la largeur de grille de la technologie FDSOI

3.3.4 Co-intégration des différents types de technologie FDSOI

3.4 Avantages de la logique asynchrone

3.5 Synthèse

4 Modélisation de la consommation d’un nœud de capteurs et de son microcontrôleur

4.1 Modèle de consommation d’un nœud de capteurs

4.1.1 Phases applicatives des nœuds de capteurs

4.1.2 Architecture du nœud modélisé

4.1.3 Mises en équation du modèle de consommation

4.1.4 Étude de cas d’un nœud de capteur

4.1.4.1 Scénario de Réception

4.1.4.2 Scénario de Mesure

4.1.5 Synthèse

4.2 Impact de l’utilisation d’un processeur de réveil

4.2.1 Architecture du microcontrôleur simulé

4.2.2 Modes de consommation du microcontrôleur

4.2.3 Spécification du processeur de réveil dans chaque phase applicative

4.3 Simulations de la consommation d’un microcontrôleur dans des scénarios de nœuds de capteurs avec et sans processeur de réveil

4.3.1 Simulations dans les différentes phases applicatives

4.3.2 Simulations dans la phase de rétention

4.3.3 Simulations dans la phase de réception, transmission et mesure

4.3.4 Simulations dans la phase de calcul

4.3.5 Simulations dans des scénarios applicatifs

4.3.5.1 Scénario avec une très faible activité

4.3.5.2 Scénario avec une activité moyenne

4.3.6 Synthèse

II Conception d’un processeur de réveil ultra basse consommation

5 Spécifications et architecture

5.1 Méthodologie de travail

5.2 Architecture partitionnée du microcontrôleur

5.3 Modèle de programmation et tâches exécutées par la plateforme de réveil

5.3.1 Tâches exécutées par le processeur de réveil

5.3.2 Programmation évènementielle

5.3.3 Exemple de programmation par machine d’état

5.4 Jeu d’instructions et spécifications

5.4.1 Architecture RISC 16 bits

5.4.2 Spécifications

5.4.2.1 Gestions des interruptions

5.4.2.2 Types de données gérées

5.4.2.3 Modes de consommation

5.4.2.4 Reset et boot du système

5.4.2.5 Périphériques de la plateforme de réveil

5.4.2.6 Débogage sur puce

5.4.2.7 Système d’alimentation

5.4.3 Jeu d’instructions

5.4.3.1 Instructions mémoire

5.4.3.2 Instructions arithmétiques et logiques

5.4.3.3 Instructions de branchements

5.4.3.4 Instructions d’appels aux fonctions

5.4.3.5 Instructions spéciales

5.4.3.6 Encodage du jeu d’instructions

5.5 Architecture de la plateforme de réveil

5.5.1 Architecture du processeur

5.5.2 Diagramme de temps d’une interruption et boucle Fetch-DecodeExecute

5.5.3 Gestion des branchements

5.5.4 Gestion de la taille des données, contenu de la mémoire de programme/données et memory map

5.5.5 Débogage sur puce du processeur

6 Microarchitecture de la plateforme de réveil

6.1 Méthode de conception asynchrone

6.1.1 Concepts de base des circuits asynchrones

6.1.1.1 Synchronisation locale entre les modules de contrôle

6.1.1.2 Caractéristiques des opérateurs asynchrones

6.1.2 Circuits asynchrones quasi-insensibles aux délais (QDI)

6.1.2.1 Porte de Muller

6.1.2.2 Exemple de propagation d’évènements dans un pipeline asynchrone et exemple de porte logique en logique QDI

6.1.3 Avantages et inconvénients de la logique asynchrone

6.1.3.1 Pipeline élastique

6.1.3.2 Circuit adapté à des évènements non déterministes

6.1.3.3 Calcul en temps minimum et temps moyen

6.1.3.4 Absence d’horloge

6.1.3.5 Consommation évènementielle et lisse

6.1.3.6 Robustesse des circuits asynchrones et souplesses d’alimentation

6.1.3.7 Augmentation de la surface du circuit

6.1.4 Exemples de description de modules asynchrones en SystemVerilog avec les outils de Tiempo

6.2 Architecture de la mémoire de programme et données

6.2.1 Caractéristiques de la mémoire

6.2.2 Protocole d’accès à la mémoire

6.2.3 Architecture de l’interface mémoire

6.2.4 Architecture des chaines de délai

6.3 Microrchitecture des modules internes

6.3.1 Contrôleur d’interruptions

6.3.2 Décodeur

6.3.3 Unité PC

6.3.4 Banc de registres

6.3.5 Bus de communication

6.3.6 Unité load – store

6.3.7 Unité arithmétique et logique

6.3.8 Unité de branchement

6.3.9 Unité de déplacement

6.3.10 Unité de support aux fonctions

6.3.11 Unité de debug

6.4 Environnement logiciel

6.5 Environnement de conception et simulation

6.5.1 Hiérarchie des modules du circuit pour la simulation mixte asynchronesynchrone

6.5.2 Flot de conception du circuit

6.6 Conclusion

7 Implémentation physique, tests, performances et consommation du processeur de réveil

7.1 Implémentation physique du circuit complet

7.1.1 Architecture globale du circuit et partitionnement des domaines de puissance

7.1.2 Architecture de la macro finale asynchrone

7.1.3 Architecture des détecteurs de fronts

7.1.4 Implémentation physique et résultats en surface

7.2 Test du circuit

7.2.1 Circuit

7.2.2 Carte de test

7.3 Programmes de test et benchmark pour microcontrôleur de nœuds de capteurs communicants

7.3.1 Drivers du circuit

7.3.2 Programmes de test pour l’estimation de la consommation du processeur de réveil

7.3.3 Benchmark pour nœuds de capteurs communicants

7.4 Performances et consommation de la plateforme de réveil et d’un circuit de comparaison

7.4.1 Estimation en performances de la plateforme de réveil

7.4.2 Estimation de la consommation de la plateforme de réveil

7.4.3 Étude du programme généré par le compilateur du WUC

7.4.4 Positionnement vis-à-vis de l’état de l’art

7.4.5 Conclusion

Conclusion générale et perspectives

Références Bibliographiques

Télécharger le rapport complet